# Is RTL Holding Back Al Hardware Generation?

Oron Port, PhD

CEO and Cofounder

DFiant

## Hypothetical AI Hardware Generation Choice

Prompt to GDS @ 99% Success

Prompt to Verilog

@ 80% Success

$t_{A@100\%} \gg t_{B@100\%}$

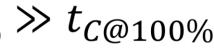

## Hypothetical Al Hardware Generation Choice

**Prompt to GDS** @ 99% Success

**Prompt to Verilog** @ 80% Success

Prompt to X @ Y% Success

$$t_{A@100\%} \gg t_{B@100\%} \gg t_{C@100\%}$$

- (Functional) Simulation Speedup

- Design Metric Optimizations:

- Performance

- Latency

- Power

- Design Partitioning:

- Embedding FPGA Cores

- Emulation and Prototyping

- Monolithic to Chiplets

### Truly Agnostic

Hardware Description Language

Meaning, not HLS nor RTL

# **Key High-Level Hardware Modeling Considerations**

Time State

Concurrency

Data

Validity

#### **HDL Alternatives**

# <u>Independent</u>

Unique syntax Inspired

Silice Spade by Rust

Veryl TL-Verilog by Verilog

SUS VHDP by VHDL

BSV PipelineC by C

<u>Dependent</u>

Clash

MyHDL, CoHDL

## **Hosted DSLs**

**DFHDL, Chisel, SpinalHDL**

Migen, Amaranth

RustHDL, RHDL

**ROHD**

**Hardcaml**

QuSoC

#### **DFHDL Design Domains**

| XX Abstraction       | Correctness  | Synthesizability | Simulation         |

|----------------------|--------------|------------------|--------------------|

| <b>DF</b> Dataflow   | Guaranteed   | Guaranteed       | Functional         |

| RT Register Transfer | Unknown<br>? | Guaranteed       | Cycle<br>Accurate  |

| ED Event Driven      | Unknown<br>? | Unknown<br>?     | <b>Event Based</b> |

class \_\_design\_name\_\_ extends XXDesign:

• Claim: "But everyone uses Verilog..."

• **Reality**: Many use custom HDLs or additional scripting to deal with Verilog's shortcomings

- Claim: "Alternative HDLs used only in Academia"

- **Reality**: Chisel-based design power SiFive IPs and several others too. SpinalHDL FPGA design worked in Space

- Claim: "Too much legacy Verilog IP"

- Counter-claim: Al can be leveraged to "decompile" legacy to alternative HDLs.

## Summary

https://dfianthdl.github.io

**Prompt to Verilog** @ 80% Success

$$t_{A@100\%} \gg t_{B@100\%} \gg t_{C@100\%}$$