## **DVT IDE**

From GVIM/EMACS to Modern IDEs: A Verification Engineer's Journey with DVT

**Netanel Miller**

Al & Verification Innovation Lead, Texas Instruments

#### **My Journey**

2012

Electrical

Engineering

at Bar Ilan

University

2016

Joined TI as Verification Engineer 2019 Technical

Leader & Founder for next-gen SOC 2020

Verification Team Leadership role 2025

Leading AI initiatives for Hardware Development

#### **Passion for innovation**

- Continuous exploration of emerging EDA tools and technologies

- Advocate for adopting transformative development methods

"Always at the intersection of hardware engineering and cutting-edge technology"

## Editor vs. IDE: Understanding the Difference

#### **Text Editor / Base IDE**

- GVIM, VS Code, Eclipse (without extensions)

- Text manipulation and syntax highlighting

- Generic project organization

#### **Hardware-Aware IDE (DVT)**

- Domain-specific intelligence

- Design hierarchy understanding

Hardware language semantics

"Editors know text; IDEs understand your design"

"The difference between typing code and engineering systems"

### **PRESENT**

## **FUTURE**

#### **The Starting Point**

- Traditional text editors (GVIM)

- Manual navigation and lookups

- Joined TI 10 years ago to this reality

#### The "Aha" Moment

- Discovery of DVT's comprehensive solution

- Design and Verification in one environment

- Intelligence-driven development

#### **Al Integration**

- DVT + VS Code + AI Copilots

- Hardware-aware artificial intelligence

- Transforming how we design systems

"A journey from text editing to intelligent design assistance"

# The DVT Advantage Features Deep Dive

Not a full demo - just my everyday essentials

## DVT's Universal Compiler Technology

### "Design with confidence - your code, any tool, any standard"

#### **Comprehensive Language Support**

IEEE HW description language standards:

- SystemVerilog (IEEE 1800-2012/2017/2023)

- VHDL (IEEE 1076-1987 through 2008)

- Specman e language (IEEE 1647-2011)

- Mixed-language environments

#### **Power Format Standards**

- UPF (IEEE 1801-2013/2015/2018)

- CPF compatibility

- Multi-power domain visualization

## Code navigation

- Hyperlink to declaration of anything:

- class, module, struct, field, method, signal, macro, `included file, ...

```

99

virtual sequencer = apb subsystem virtual sequencer::type id::create("virtual sequencer",this);

= ahb pkg::ahb env::type id::create("ahb0",this);

100

ahb0

101

= apb pkg::apb env::type id::create("apb0",this);

Open Declaration

= uart pkg::uart env::type id::create("uart0",this);

102

103

Open Field Type

= uart pkg::uart env::type id::create("uart1",this);

104

= spi pkg::spi env::type id::create("spi0",this);

Show Usages

= gpio pkg::gpio env::type id::create("gpio0",this);

105

```

```

32 class apb_subsystem_tb extends uvm_env;

33

34 apb_subsystem_virtual_sequencer virtual_sequencer; // multi-channel sequencer

35 ahb_pkg::ahb_env ahb0; // AHB UVC

36 apb_pkg::apb_env apb0; // APB UVC

```

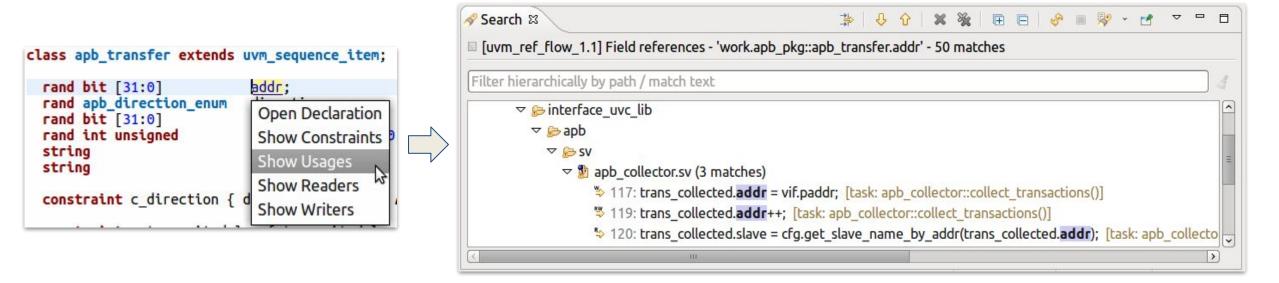

## Code navigation

- Hyperlink to declaration of anything:

- class, module, method, signal, macro, `included file, ...

- Show usages of anything:

- Readers / Writers of any variable / signal

- Constraints of a rand class variable

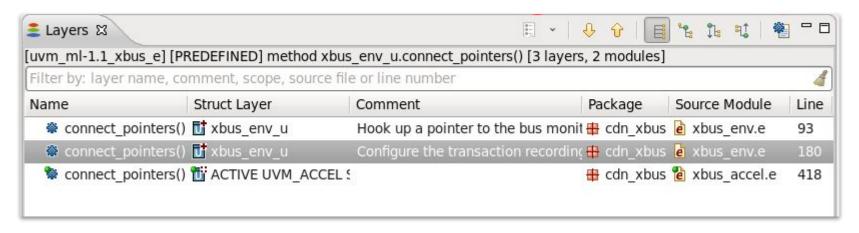

## Code navigation

- Hyperlink to declaration of anything:

- class, module, method, signal, macro, `included file, ...

- Show usages of anything:

- Readers / Writers of any variable / signal

- Constraints of a rand class variable

- "Layers" of types, structs/units, methods, events, covergroups, ... (e Language;)

## Auto-complete

- Context-sensitive: NOT textual proposals, only valid completions

- class\_variable . <shows fields, methods, constraints, ... in the class>

- e\_port . <shows hdl\_path(), put\_mvl(), agent(), ...>

- enum\_variable == <shows only enum values>

```

*xbus accel.e ×

b xbus signal map h.e

UVM ACCEL xbus signal map u

5869

connect ports() is also {

587

sig start.disconnect();

do bind (sig start, empty);

588

$589

sig addr.disconnect();

$590

do bind (sig addr, empty);

©591

sig addr.di

do_bind (si o Show AI Assistant Code Completions ...

⇒592

method any port.disconnect

593

do_bind (si @ disconnect()

594

sig read.di * disconnect bound set()

PREDEFINED

595

596

do_bind (si * vhdl_disconnect_value(): list of mvl

Disconnect a port from its bound set.

sia write.d

597

Calling this pseudo-method of a port disconnects this port from the bound set it

do hind (si

598

belongs to, and returns it to its initial, dangling state. The rest of the bound set

remains intact.

→ d cdn xbus → d UVM

```

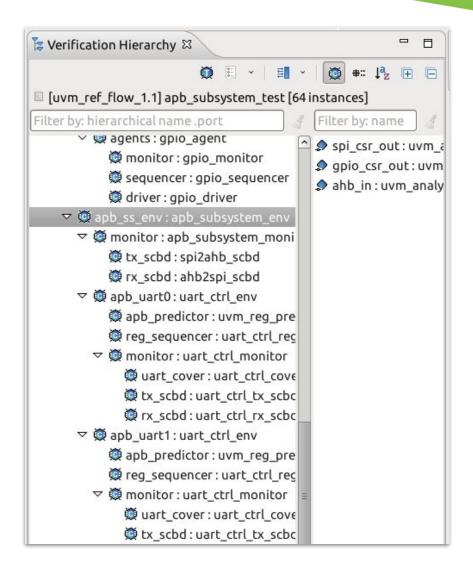

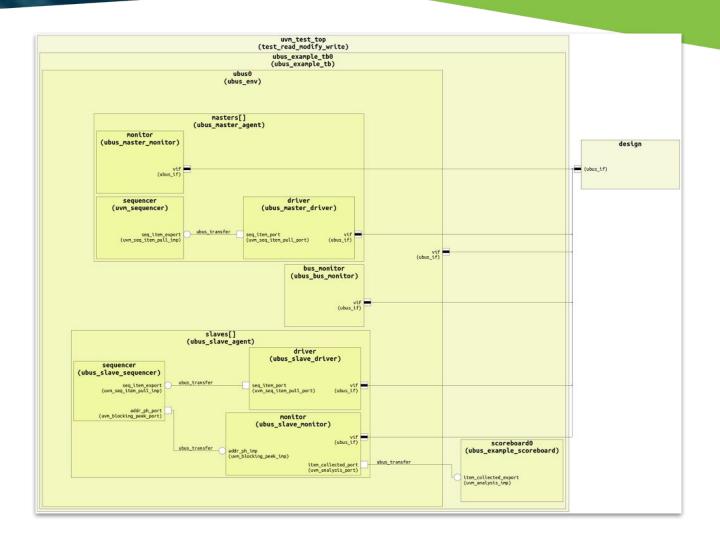

- Perform UVM Runtime Elaboration

- Verification Hierarchy

- Browse & search accurate test topology

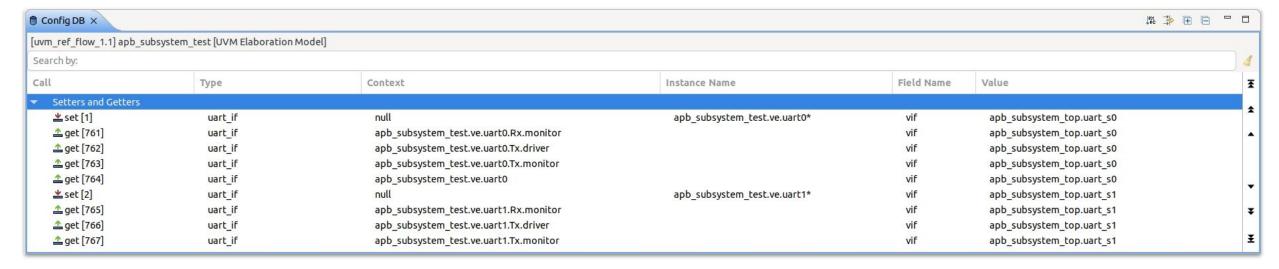

- Perform UVM Runtime Elaboration

- Verification Hierarchy

- Config DB

- Browse config\_db set/get calls

- Inspect DB values

- Perform UVM Runtime Elaboration

- Verification Hierarchy

- Config DB

- Browse config\_db set/get calls

- Inspect DB values

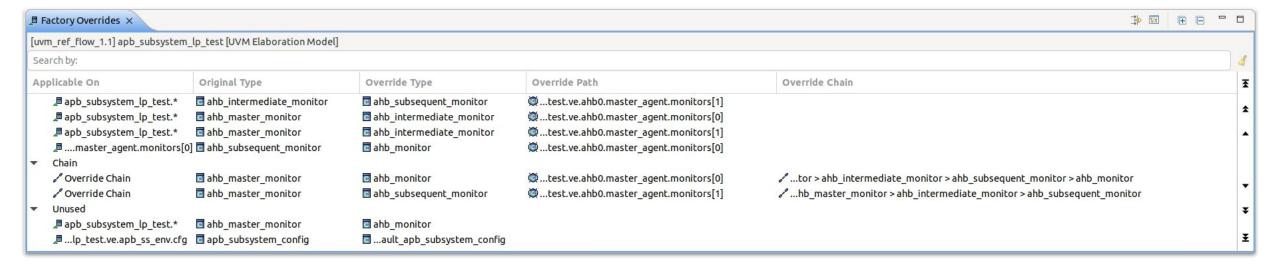

- Factory Overrides

- Untangle overrides applied by the UVM factory

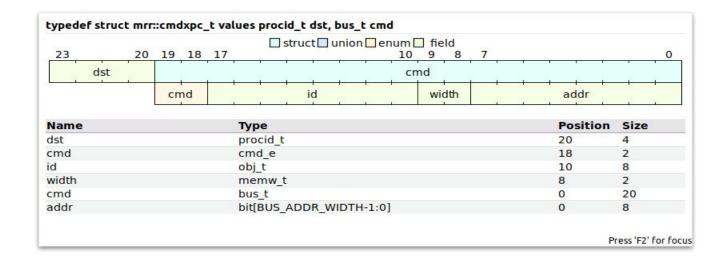

- Perform UVM Runtime Elaboration

- Verification Hierarchy

- Config DB

- Browse config\_db set/get calls

- Inspect DB values

- Factory Overrides

- Untangle overrides applied by the UVM factory

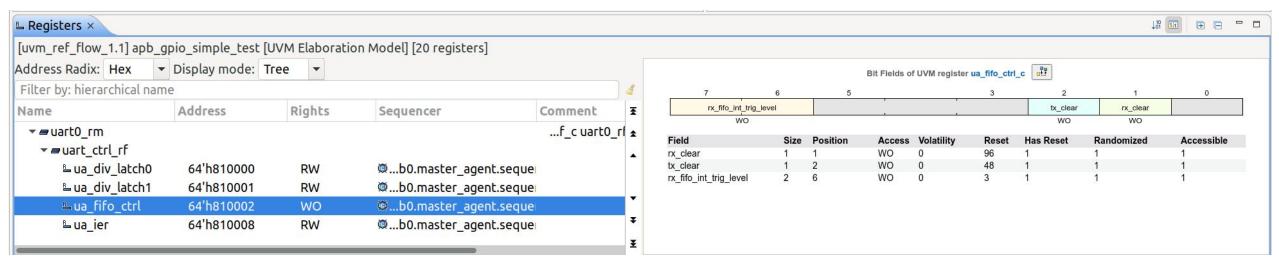

- Registers

- Browse reg blocks

- Visualize reg bitfields

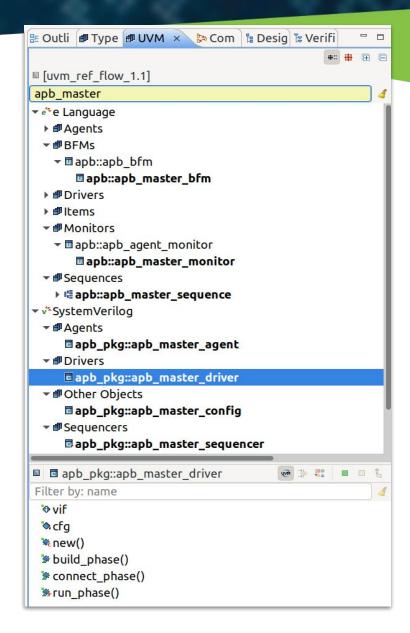

## **UVM Support**

#### UVM Browser

- UVM based classes grouped by category

- Mixed-language SV & e Language

- UVM flow specific API

- Overridden phases

- Factory registered fields

- TLM ports

#### UVM Browser

- UVM based classes grouped by category

- Mixed-language SV & e Language

- UVM flow specific API

- Overridden phases

- Factory registered fields

- TLM ports

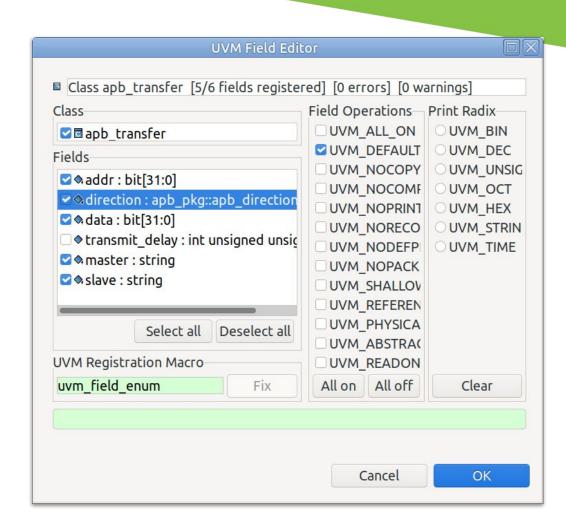

#### UVM Field Editor

- Inspect and edit UVM field registrations

- Auto-detects correct macro for each field

- Design Hierarchy View

- No need to open the simulation

- Quick search (by instance name, by hierarchy, by port name)

- Track elaborated param values

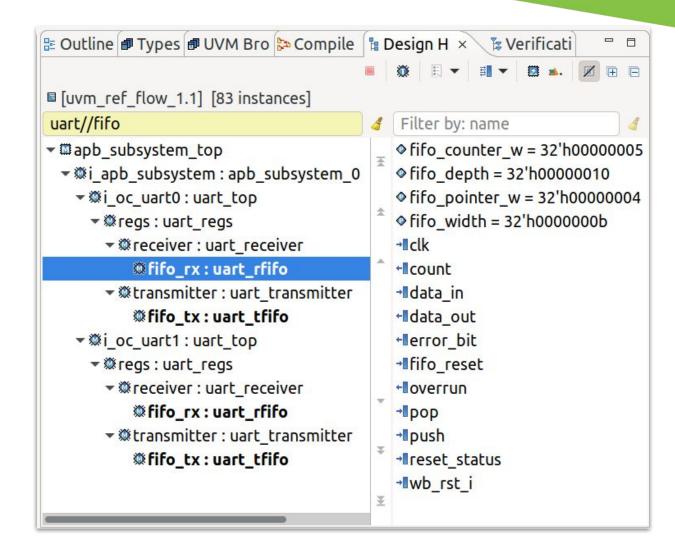

#### Design Hierarchy View

- No need to open the simulation

- Quick search (by instance name, by hierarchy, by port name)

- Track elaborated param values

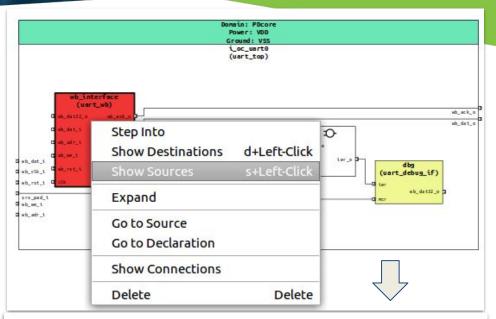

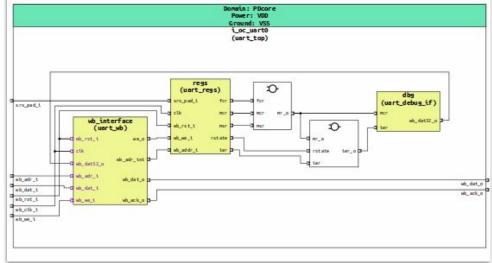

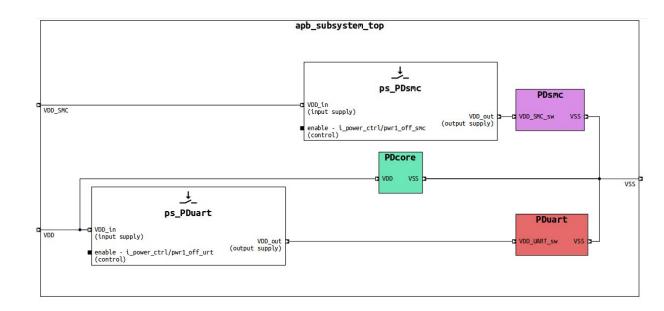

- Schematic Diagrams

- Show ports, sub-instances, logic blocks and connections

- Customizable (filters, colors)

- Allows step by step tracing

#### Design Hierarchy View

- No need to open the simulation

- Quick search (by instance name, by hierarchy, by port name)

- Track elaborated param values

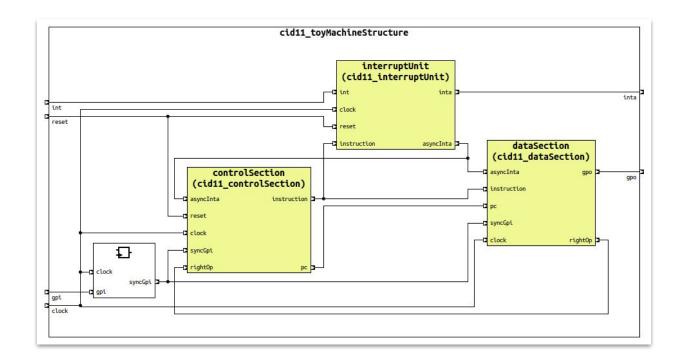

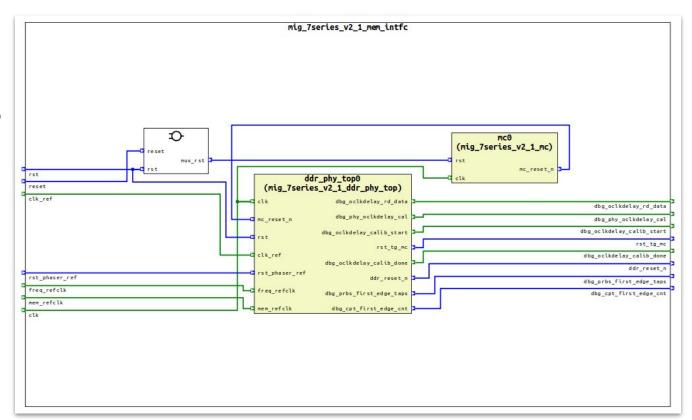

#### Schematic Diagrams

- Show ports, sub-instances, logic blocks and connections

- Customizable (filters, colors)

- Allows step by step tracing

#### Design Hierarchy View

- No need to open the simulation

- Quick search (by instance name, by hierarchy, by port name)

- Track elaborated param values

#### Schematic Diagrams

- Show ports, sub-instances, logic blocks and connections

- Customizable (filters, colors)

- Allows step by step tracing

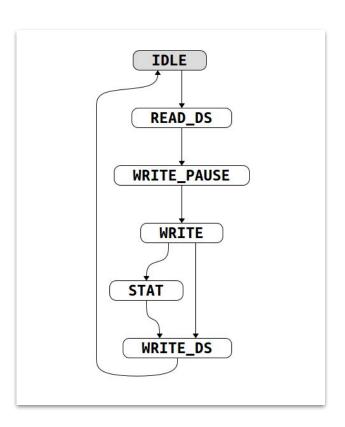

## Code Visualization

- Many other types of diagrams:

- Wavedrom Timing Diagrams

- FSM Diagrams

- UVM Component Diagrams

- Bitfield Diagrams

## Code Visualization

- Many other types of diagrams:

- Wavedrom Timing Diagrams

- FSM Diagrams

- UVM Component Diagrams

- Bitfield Diagrams

- Many other types of diagrams:

- Wavedrom Timing Diagrams

- FSM Diagrams

- UVM Component Diagrams

- Bitfield Diagrams

## Code Visualization

- Many other types of diagrams:

- Wavedrom Timing Diagrams

- FSM Diagrams

- UVM Component Diagrams

- Bitfield Diagrams

#### Smart Log

- Jump from sim log to code

- Messages color-coded by UVM component

- Errors collected as part of the Problems view

```

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(227) @ 35151000: uvm test top.ve.uart0.Rx.monitor [uart rx monitor] Received a Stop bit: 'b1

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(211) @ 35151000: uvm test top.ve.uart0.Tx.monitor [uart tx monitor] Received a Frame data bit:'b0

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(236) @ 35950000: uvm test top.ve.uart0.Rx.monitor [uart rx monitor] Collected the following Frame No:1

Size Value

Name

uart frame

uart frame

@14998

start bit

'h0

integral

'hcf

payload

integral

'h1

parity

integral

stop bits

integral

'h1

error bits

integral

parity type

parity e

GOOD PARITY

transmit delay

'd22

integral

begin time

18750000

UVM ERROR uart ctrl/sv/uart ctrl scoreboard.sv(196) @ 35950000: uvm test top.ve.apb ss env.apb uart0.monitor.rx scbd [SCRBD] ###### FAIL : uart0 RECEIVED WRONG DATA

UVM INFO wart ctrl/sv/wart ctrl scoreboard.sv(197) @ 35950000: wvm test top.ve.apb ss env.apb wart0.monitor.rx scbd [SCRBD] expected = 'hcf, received = 'hcf

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(175) @ 35950000: uvm test top.ve.uart0.Rx.monitor [uart rx monitor] trying to detect SOP

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(227) @ 35951000: uvm test top.ve.uartl.Rx.monitor [uart rx monitor] Received a Stop bit: 'b1

UVM INFO interface uvc lib/uart/sv/uart monitor.sv(236) @ 36750000: uvm test top.ve.uart1.Rx.monitor [uart rx monitor] Collected the following Frame No:1

```

192 193

194

195⊜

196

197 198 else

begin

endfunction : write uart

if ((temp1 & mask) == frame.payload)

`uvm info("SCRBD", \$psprintf("###### PASS : %s RECEIVED CORRECT DATA

`uvm\_error("SCRBD", \$psprintf("####### FAIL : %s RECEIVED WRONG DATA" `uvm info("SCRBD", \$psprintf("expected = 'h%0h, received = 'h%0h", ter

#### Smart Log

- Jump from sim log to code

- Messages color-coded by UVM compone

- Errors collected as part of the Problems

#### Macro expansion

- Inline expansion & quick collapse

- Also visible in Inspect View

- See values in tooltips

```

`uvm_component_utils (spi2ahb_scbd)

uvm_analysis_imp_ahb

uvm_analysis_imp_spi

function new (string

super.new(name, pa

spi_add = new("sp

ahb_match = new("a

endfunction : new

```

```

@DVT EXPAND MACRO INLINE START

// 'uvm component utils(spi2ahb scbd)

// @DVT EXPAND MACRO INLINE ORIGINAL

static bit m registered converter = m uvm resource sprint converter#(spi2ahb scbd)::register();

typedef uvm component registry #(spi2ahb scbd, "spi2ahb scbd") type id;

static function type id get type();

return type id::get();

endfunction

virtual function uvm object wrapper get object type();

return type id::get();

endfunction

const static string type name = "spi2ahb scbd";

virtual function string get type name ();

return type name;

endfunction

@DVT EXPAND MACRO INLINE END

```

## Low power format (UPF)

- Power Domain View shows

- Design instances

- Isolation strategies

- Retention rules

- Power domains also shown in

- Design Hierarchy View

- Schematic Diagrams

- Breadcrumb Navigation Bar

- Supply Network Diagram

## **The Evolution Continues**

## DVT + VS Code + AI

## DVT in the VS Code Era

#### Modern Development Environment

- The Power of Integration

- DVT now available as a VS Code plugin

- Industry-standard development environment

- Complete hardware design & verification capabilities in a modern IDE

#### VS-Code One Environment, Many Tools

## AMIQ's Built-In AI Assistant

- Smart Assistance for Hardware Design

- AMIQ's built-in Al assistant for DVT users

- Hardware-aware code suggestions and completion

- Specialized for HDL and verification languages

- Connects to your company's LLM infrastructure

"Al assistance tailored specifically for hardware engineers"

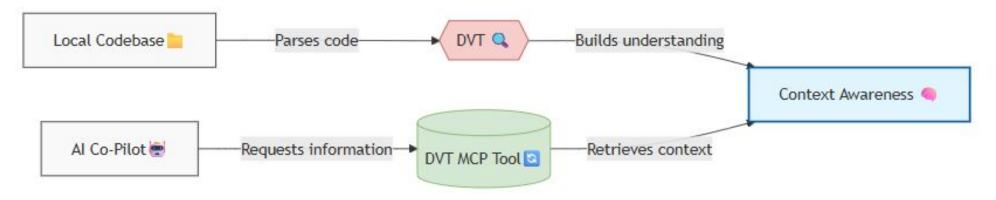

## MCP - Making Al Understand Your Code

- Bringing Al Intelligence to Your local codebase

- Upcoming MCP tools connect your codebase with AI assistants

- Your AI assistant becomes familiar with your specific codebase

- Works alongside external AI Copilots for advanced assistance

- Maintains privacy while enabling powerful completions

Bridges the gap between generic AI and hardware-specific knowledge

#### **Contact me for further details**

Email: miller2812@gmail.com

<u>Phone</u>: 054-6442812 <u>LinkedIn</u>: <u>Netanel Miller</u>