**Lee Harrison Marketing Director, Siemens EDA, Tessent**

#### Semiconductor companies are facing key challenges

#### **Increasing engineering hours**

#### **Shrinking talent base**

Shortage of **semiconductor workers** in US by 2030

#### **Increasing development costs**

Estimated first-time total SoC design cost or 3 nm node

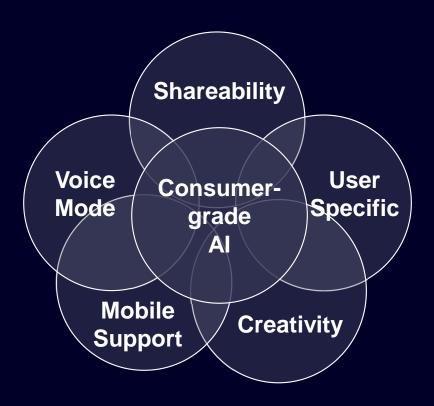

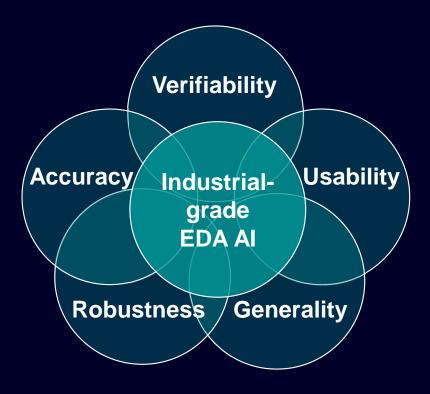

#### EDA Al needs to be industrial-grade Al for deployment in production

#### **Elements for consumer Al**

#### **Elements for EDA AI**

#### An EDA Al system should be purpose-built

#### **Expertise**

Analyze thousands of documents & synthesize critical EDA insights to quickly resolve your queries

#### **Accelerated Design**

Generate scripts, configurations, designs, and tool automations for faster design cycles

#### **Faster Verification**

Speed up testbench generation, verification, and signoff for shorter time-to-market

#### An EDA Al system should be augmented to support EDA modalities

#### **Traditional modalities of LLMs**

#### **EDA-focused modalities (~50 formats)**

**Text**

**Image**

Audio

Verilog & Netlists (10+ formats)

GDSII / OASIS (5+ formats)

Liberty (5+ formats)

Code

Tables

Simulation Data (~5 formats)

**Proprietary Design Languages**

**Binaries** (10+ formats)

Miscellaneous (10+ formats)

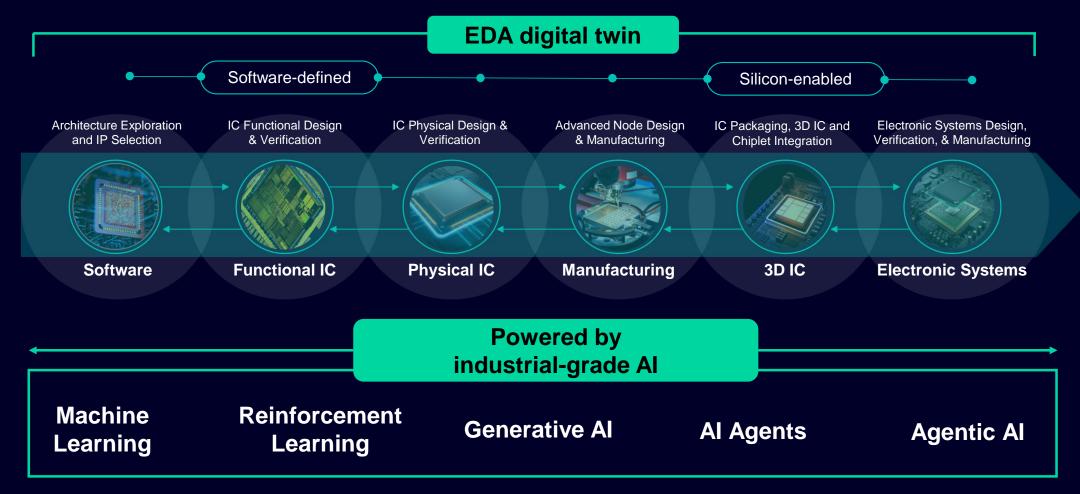

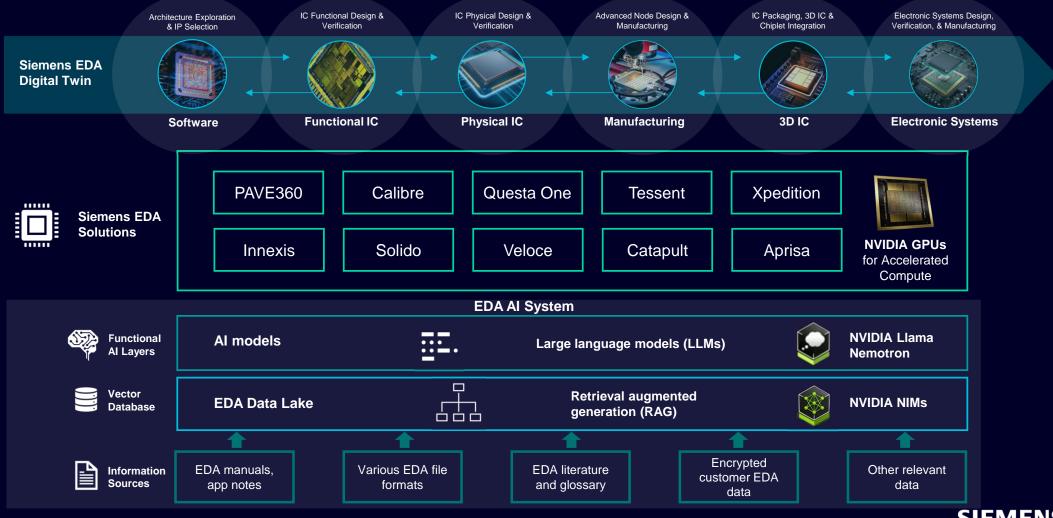

## An EDA Al system should be modular, flexible and quickly adapt to improving foundation technology

#### An EDA AI system has specific characteristics and needs to be built on three pillars

### **Scalable** Intelligence

- Support for multiple LLMs

- Fine-tuning is optional

- ML/RL capabilities

- Fast inference times

- · Hardware agnostic deployment

### Secure and **Flexible**

- · Centralized multimodal data lake

- Able to build custom workflows

- On-premise/cloud support

- Enterprise-grade security

- Customizable access controls

### **User-centric Design**

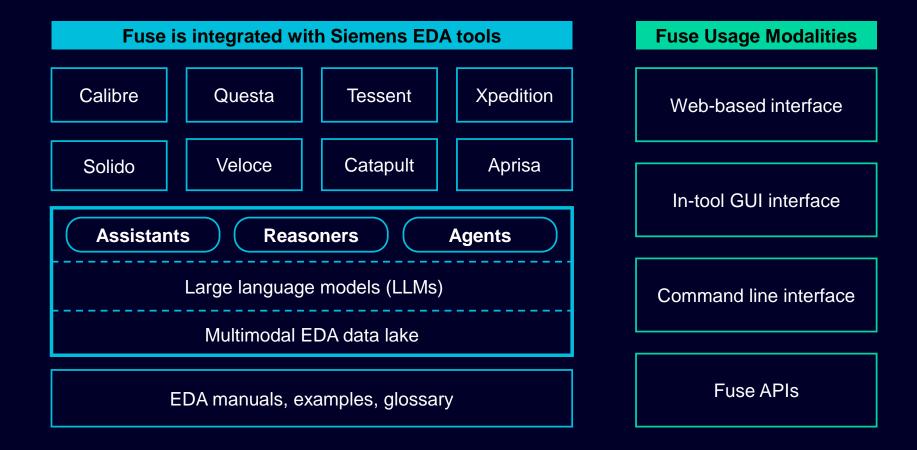

- Integrated with designer workflows (CLI, GUI, web)

- Multiple EDA modality support

- Seamless EDA integration

- Automated workflow capabilities

- Data flywheel

#### An EDA Al system should have a range of capabilities

#### **Assistants**

Quickly answer queries about EDA documents, tools, workflows, etc.

#### Reasoners

Follow a multi-step thinking process to intelligently analyze log files, netlists, RTL, etc.

#### **Agents**

Natural language-based automation and tool calling for variety of tasks

#### An EDA AI system should span across the entire semiconductor and PCB systems workflow

#### **Siemens EDA announces EDA AI System**

#### Enables generative and agentic Al capabilities across the EDA workflow

#### **NVIDIA** hardware and software stack turbocharges Siemens EDA portfolio

Page 12 Unrestricted | Semisrael | Siemens EDA SIEMENS

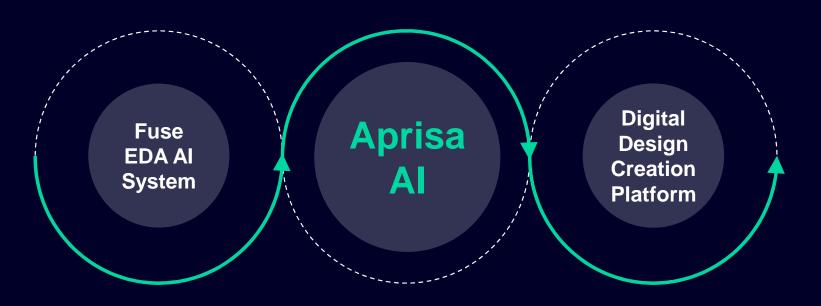

# Aprisa Al

#### Aprisa AI expands from differentiated ML / RL tools to centralized Gen AI and agentic flows

**Core ML / RL: Al design explorer** identifies &

implements best QoR flows

Gen Al: Fuse integration boosts productivity, enables rapid ramp up

Al agents deliver automation to massively scale engineering efforts

Aprisa AI delivers 10X productivity boost, 3X improved compute-time efficiency, and 10% better PPA for RTL-to-GDS

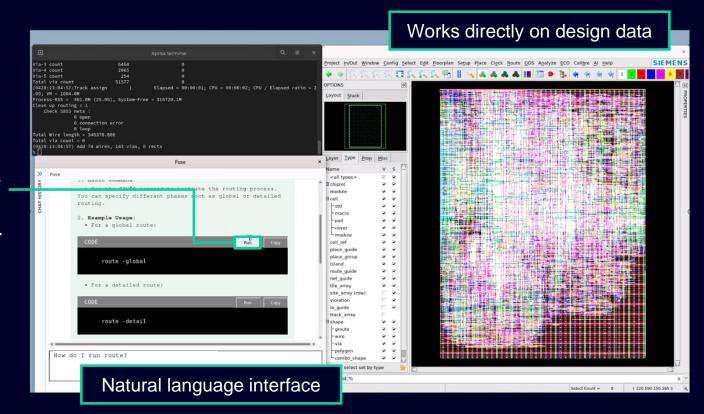

## Aprisa's built-in Fuse integration provides a natural language interface to verifiable answers within Aprisa

#### **Built-in Fuse integration**

- Tool know-how, best practices, commands available via natural language, without leaving Aprisa

- Realtime command execution: Directly run commands suggested by Fuse

- All sources displayed at end of answer

Augments design team expertise and enables rapid ramp-up

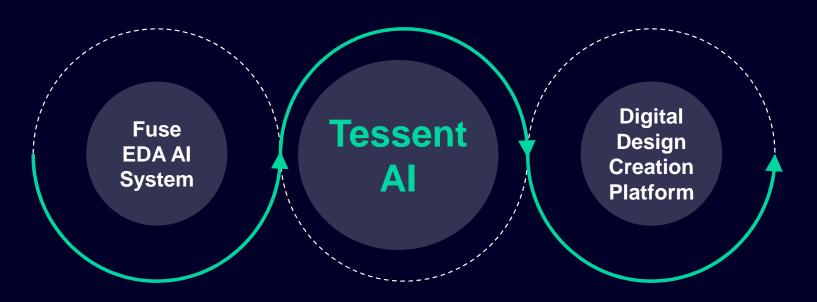

# Tessent Al

## Tessent AI expands from differentiated ML / RL tools to centralized Gen AI and agentic flows

**Core ML / RL: Al ATPG optimizations** provides fault weighting to reduce test time and test pattern efficiency

**Gen Al: Fuse integration** boosts productivity, enables rapid ramp up

Al agents deliver detailed DRC feedback and auto DRC fixing

Tessent Al delivers 5X ATPG generation time speed up, and significant reduction in test time

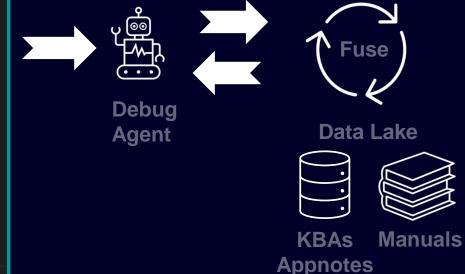

#### Aid in DFT debug

#### Traditional method

- Search for error code in documentation

- Determine which set of instructions apply to current design/mode

- Follow instructions might require running a set of command or tools like Visualizer

#### With Gen Al agent

- User asks AI debug assistant how to resolve the error

- Phase I: **Al assistant** suggests necessary steps specific to current design/mode. User then follows instructions.

- Phase II: Al agent automatically runs some of the commands

/ tools needed for debugging and presents results

**SIEMENS**

# Thank you!

For more information about this presentation, please contact

Lee Harrison (lee.harrison@siemens.com)